A look back at RISC-V Development Timeline in 2020

RISC-V is a unique computing instruction set that offers innovative operational mechanisms, developed in 2010, this year marks its 10th Anniversary. RISC-V Foundation has also found great success this year as its technical community has grown 66 per cent to more than 2,300 individuals in more than 50 technical and special interest group.

Calista Redmond, CEO of RISC-V International, has mentioned that they ” saw an increased momentum of RISC-V cores, SoCs, developer boards, software and tools across computing from embedded to enterprise. Thus, here we will compile RISC-V’s news and development in the year 2020.

Timeline

Jan ’20: ESP enables design RISC-V with accelerators

- ESP (Embedded Scalable Platform) will support 64-bit Ariane (RISC-V) cores, with a seamless accelerator design flow that allows FPGA development boards to run it.

Ref: ESP Open Source Research Platform Enables the Design of RISC-V & Sparc SoC’s with Accelerators

March ~ May ’20: New member incorporated RISC-V International Association, An Open Approach to System Security, Partnerships

- RISC-V International was incorporated in Switzerland, which allowed RISC-V to shift to a more inclusive membership structure.

- RISC-V is facing challenges where bugs and security issues literally cannot be backtracked due to the opacity and lack of transparency of hardware source code from hardware vendors.

- The RISC-V Foundation has decided to step up and take action to make a significant leap toward improving transparency in hardware designs.

- The RISC-V Architecture Test Working Group initiated a compatibility framework and tests to help developers ensure their solutions are in accordance with the specification.

- Additionally, RISC-V International and GlobalPlatform, the standard for secure digital services and devices, announced a partnership to help accelerate the development of open standards that simplify security design for hardware developers and enhance the security of Internet of Things (IoT) devices and processors.

- RISC-V is also creating a security response process to better respond to potential security issues and innovative cryptography extensions to enhance performance in secure deployments.

Ref: History of RISC-V, RISC-V International Partners with GlobalPlatform to Simplify Security Design for IoT Devices and Processors

May ~ June ’20: RISC-V Cores spotlight, New Partnerships, Expanding Leadership team

- COVID-19 pandemic has given RISC-V new opportunities to prove they can help engineers develop chips without worrying about funding.

- Focused on ratifying extensions, identifying and addressing opportunities and gaps, and expanding collaboration and development across markets to strengthen the community and access to RISC-V resources.

- Along with a new processor trace specification, another RISC-V development comes from SiFive, which has pledged to open access to its intellectual property (IP), so designers can help fight COVID-19.

- A new partnership between GigaDevice and IAR Systems brings professional Dev Tools to RISC-V Microcontrollers

- Mark Himelstein appointed as CTO to work with the RISC-V technical community.

- Kim McMahon appointed as Director of Marketing to increase the visibility of RISC-V and amplify the growing industry momentum of their member community.

- GAP9 RISC-V for ML at the Edge: GreenWaves GAP9 updated its Predecessor RISC-V CPU.

- GAP9 comes with the previous eight RISC-V cores of GAP8 with custom ML acceleration functions. The nine cores run in a 128KB block of SRAM, and there is an unusual 1.5MB interleaved memory block (for coefficient design) and a 128KB block (for encoding) combined.

Ref: COVID-19 Puts Spotlight on Open-Source RISC-V Cores, IP, A New Partnership Brings Professional Dev Tools to RISC-V Microcontrollers, New RISC-V Director of Marketing: Increasing Visibility of the RISC-V Revolution, Welcome Mark Himelstein, RISC-V International CTO!

July ~ August ’20: SiFive unveils major upgrades to RISC-V-Based Processors, celebrates 10th Birthday

- The improvements SiFive focused on within this release were power, performance, and area (PPA). Thus, the level-up on processors could have significant implications for custom SoC design.

- The SiFive 20G1 release has enhanced the cores of the SiFive Core IP line by lowering the power consumption, decreasing the area, and increasing the performance.

- As RISC-V Foundation recounts their history and showed their value in open-source design that has led to significant developments in the industry, they show no signs of slowing down.

Ref: SiFive Elevates Custom SoC Design With Enhanced Processor IP Portfolio, RISC-V: Standing on the Shoulders of Giants, RISC-V Celebrates 10 Years of Open-Source ISA

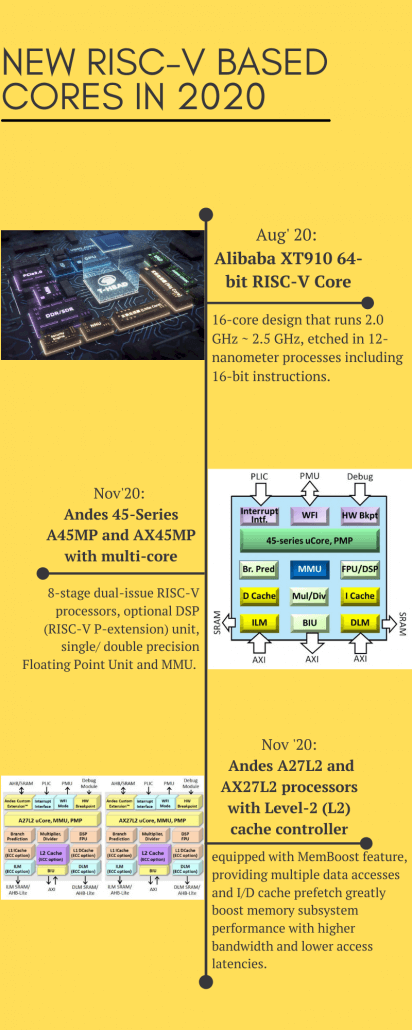

New RISC-V based cores

There are many new RISC-V based cores this year, but to name a few notable core releases, we have:

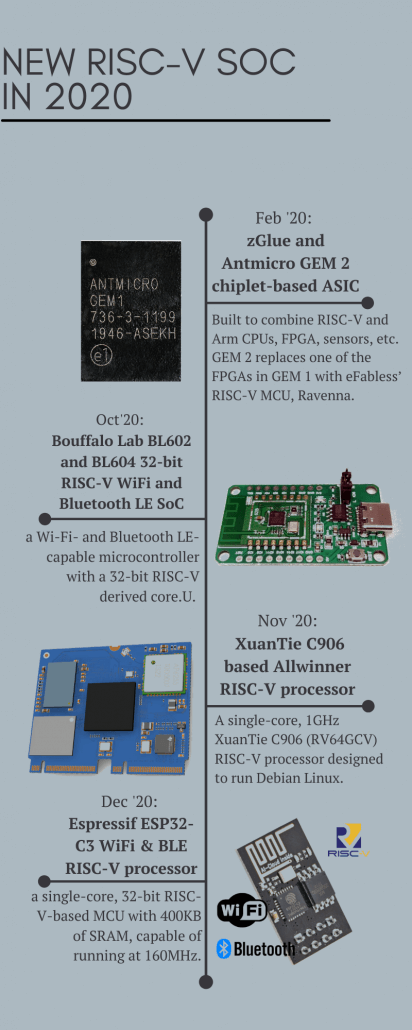

New RISC-V SoC

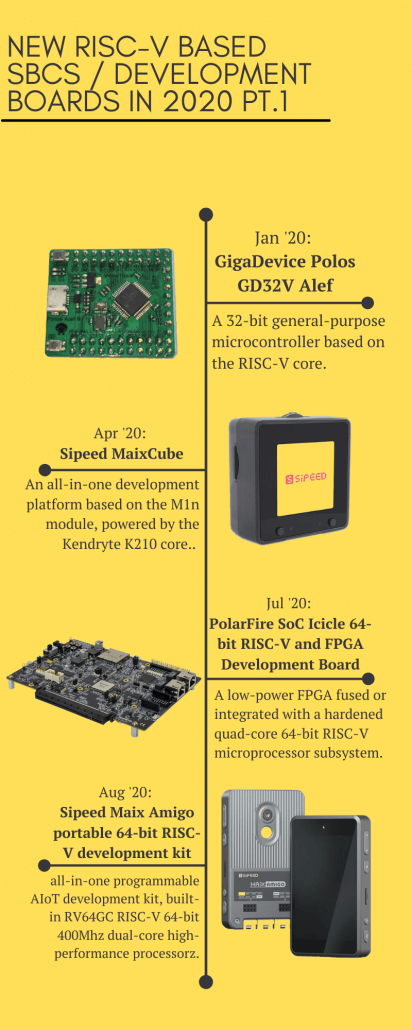

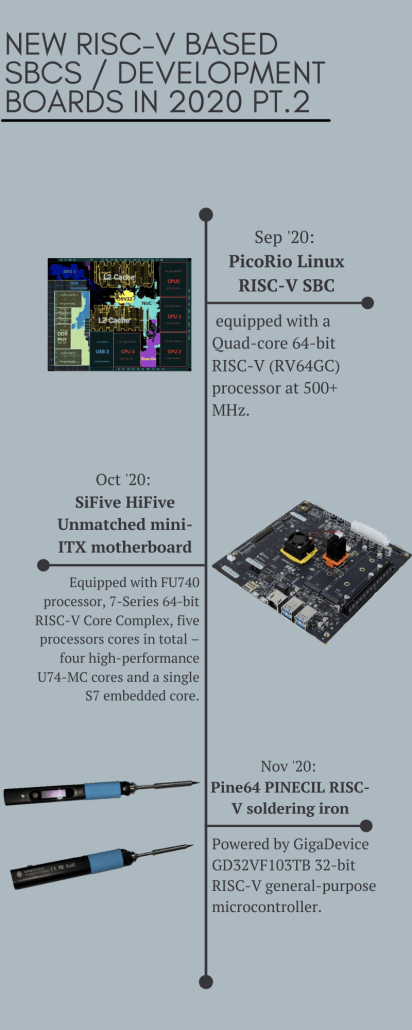

New RISC-V based SBCs / Development Boards

If you’re interested in the Sipeed products that are mentioned here, we do carry them at Seeed as well! So feel free to check them out:

What else?

- RISC-V International has launched three new learning programs, including the RISC-V Training Partner Program, Learn online, and university alliances to extend the breadth and reach of RISC-V knowledge, provide opportunities for a broader audience to teach and learn, and engage the community to achieve expertise in the critical areas needed for a healthy ecosystem.

- One of the courses that were recently unveiled is the Imagination University Programme (IUP) course “RVfpga: Understanding Computer Architecture.” It is currently available in English, and a Chinese version will be available in early 2021.

Summary

Surely, the RISC-V Foundation will definitely continue to prosper and contribute more exciting innovations for us in the upcoming years, their 10th year is just the beginning and we can’t wait to see what else they have in store for us!

If you’re interested in more RISC-V related articles, do check out the other ones down below!

- What is RISC-V?10 Things You Should Know About RISC-V in 2020

- RISC-V Open-source Hardware and Resource Roundup at Seeed Studio