What is RISC-V?10 Things You Should Know About RISC-V in 2020

What is RISC-V

RISC-V is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles.

Unlike most other ISA designs, the RISC-V ISA is provided under open source licenses that do not require fees to use.

A number of companies are offering or have announced RISC-V hardware, open-source operating systems are available and the instruction set is supported in several popular software toolchains.

Two Kinds of ISA(CISC vs RISC)

CISC – Complex Instruction Set Computer

The CISC contains not only the common instructions of the processor but also a lot of uncommon instructions (the 28th principle, 80% of the instructions used in the program operation, only 20% of all instructions.

There are many instructions, the typical representative is Intel’s x86 architecture. x86-64 is a 64-bit extension of the x86 architecture, designed by AMD and also known as AMD64.

RISC – Reduced Instruction Set Computer

Reduced instruction set architecture contains only the instructions commonly used by the processor. For less commonly used operations, the same effect can be achieved by executing multiple commonly used instructions. The reduced instruction set represents more MIPS, RISC-V, Power, Alpha, etc.

Why does Instruction Set Architecture Matter?

The ISA somehow decides the application. It is common sense that the world’s most famous 2 ISA are X86 architecture and ARM architecture. Their application fields are totally different.

99%+ of laptops, desktops, and servers are based on X86 or AMD64 ISA. The IPs belong to Intel and AMD.

99+ mobile phones and tablets are based on ARM ISA, and the IPs are divided into A series, R series, and M series.

While RISC-V is very suitable for use in some specific application fields such as storage, edge computing, and AI applications.

The different applications field makes it possible for RISC-V to compete with ARM and X86.

What’s Different About RISC-V?

Compared to ARM and X86, RISC-V has below advantages:

Free: RISC-V is open-source, there is no need to pay for the IP.

Simple: RISC-V is far smaller than other commercial ISAs.

Modular: RISC-V has a small standard base ISA, with multiple standard extensions.

Stable: Base and first standard extensions are already frozen. There is no need to worry about major updates.

Extensibility: Specific functions can be added based on extensions. There are many more extensions are under development, such as Vector.

ISA Base and Extensions of RISC-V

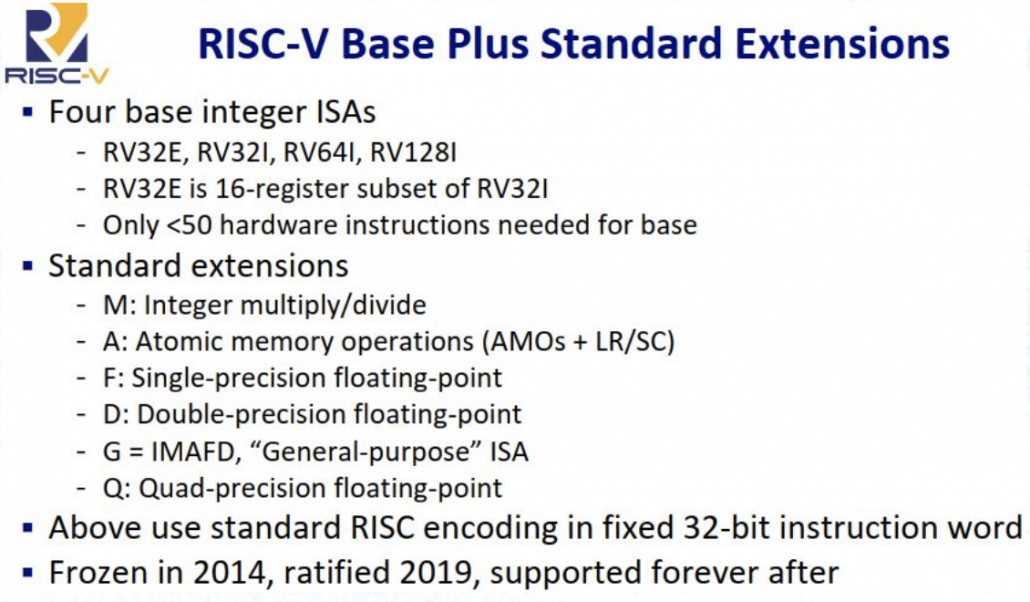

As mentioned earlier, the RISC-V instruction set has modular characteristics. The instruction set is organized in a modular manner. Each module is represented by an English letter.

The instruction set includes the standard part and the extension part. The standard part must be implemented.

For example:

If you want to implement a 32-bit architecture RISC-V processor, the RV32I instruction set must be implemented on the hardware (machine mode must also be implemented in privileged mode).

The basic integer ISA and the machine privilege ISA provide the functions required by the basic general-purpose CPU. Developers can also enhance the processor’s functionality by adding extensions to ISA. There are already many standard extensions, such as the approved MAFDGQ.

What’s the downside of RISC-V?

While there are many advantages of RISC-V, as a new player, there are some downsides that users will need to take into consideration when using it.

The compatibility of different RISC-V ISAs. Since RISC-V is open source, there will be more and more IPs based on RISC-V, the RISC-V Foundation will need to make sure there is only one standard.

The ecosystem is not mature enough. It needs a lot of around the ISA to design a real chip, while the RISC-V will have to re-create or at least adopt all the chip design ecosystems that a dominant ISA already has for a very long time.

It still takes time for implementation. Even though there are a lot of RISC-V SoCs working fine under some applications, it is still a long way to verify and optimize the implementation in real-life applications.

Linux on RISC-V, what’s the latest stage?

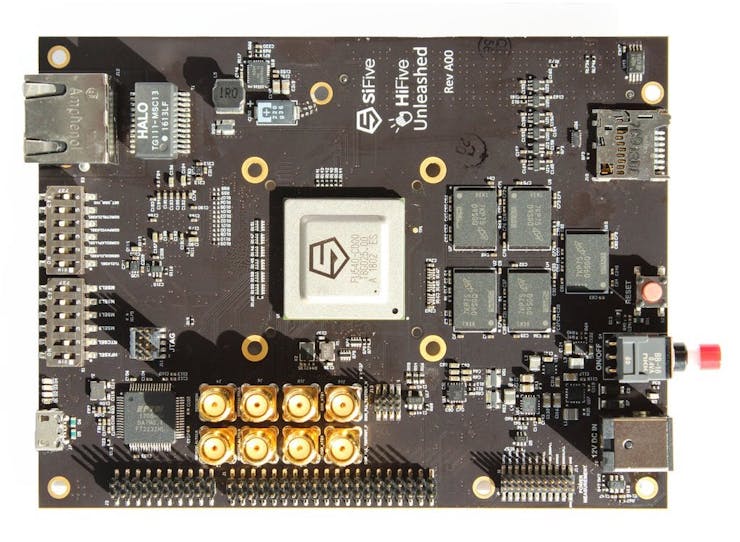

Back in 2018, SiFive, one of the most active members of the RISV-V Foundation, has already released a board called HiFive that was capable of running Linux on it.

Despite the price being up to $999, it is still quite an exciting board for the community.

In 2020, with the development of Linux on RISC-V, we have seen an implementation of Linux NOMMU version on the Kendrtyte K210, a RISC-V SoC that is under $10.

Although there is only 8MB RAM and no MMU, this has still become a big encouragement for the community.

As a member of the Open Source community, Seeed has a series of products based on the Kendryte K210 sold on the online store, such as the MAix Bit, the Maixduino Kit, and the Grove AI HAT for Raspberry Pi.

How Many RISC-V SoCs have been implemented?

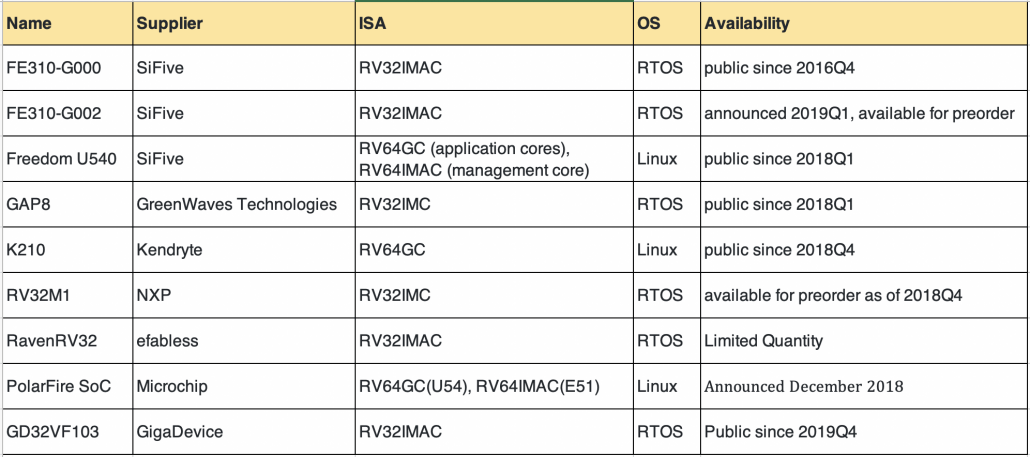

From the information of RISC-V GitHub, there are at least more than 13 commercial implementations for RISC-V, and 9 SoCs have been released, which include solutions from companies like Gigadevice, GreenWave, and SiFive.

For those companies mentioned above, Seeed has also provided development boards. Such as the Wio Lite RISC-V, incorporating the GD32 from Gigadevice.

The RISC-V International Association Has Been Incorporated in Switzerland

Although the RISC-V project was initially created in the US, although there have not been any export restrictions on RISC-V in the US and they have complied with all US laws, the association still decided to move out of the US, in order to alleviate uncertainty going forward.

So in March 2020, the RISC-V international association has been officially incorporated in Switzerland. And there are already 500+ members.

It is RISC-V 10 Years Birthday

It is hard to believe that the RISC-V five project is ten years old. It is only recently, from the official announcement of the RISC-V Foundation, that we know that the project was started in 2010.

“After careful perusal of old email files, we’ve decided that May 18th, 2010, was the day when we finally decided to develop our own clean-slate ISA, and so we’re using this as the official birthday of RISC-V, even though the actual name came a bit later.”

It is very exciting to see for only 10 years, RISC-V has achieved so many things and is still growing fast. RISC-V is bringing a revolution to the world, let’s evolve in the revolution, and looking forward to more things that RISC-V will bring to us.